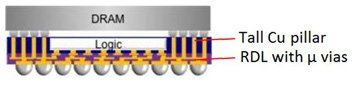

FO- Package-on-Package example for advanced processor application

Source: Yole Development, “Fan-out packaging, technologies and market trends”, Release 2016

BERLIN, 12. May, 2017: Atotech, a global leader in specialty plating chemicals, equipment and services will present its next generation plating technologies for FO-Panel Level Packaging (FO-PLP) at the upcoming ECTC 2017, held from May 30 to June 2, 2017, at the Walt Disney World Swan and Dolphin Resort in Florida, USA. Atotech’s specialists’ also co-authored work on fine pitch flip chip process technologies and 3D Cu-Cu and micro bump bonding technologies which will be presented as collaborative work at ECTCs program sessions.

In an interactive presentation on May 31, 2017, from 9 to 11 am, Ralph Zoberbier, Manager Equipment Sales and Marketing at Atotech Deutschland GmbH, will present next generation plating technologies for FO-Panel Level Packaging. In his presentation, Ralph Zoberbier will highlight the current manufacturing challenges in panel based packaging applications and present Atotech’s latest technology developments and solutions on its MultiPlate® equipment and plating processes, dedicated for next generation FO-PLP.

Work co-authored by Atotech’s specialists will be presented at the following program sessions:

- Session 9: Fine pitch flip chip process technologies, at 1:55 pm on May 31, on “Scaling Cu pillars to 20µm pitch and below: Strategic role of surface finish and barrier layers” and

- Session 21: 3D Cu-Cu and micro bump bonding technologies, at 1:30 pm on June 1, on “Morphology study of bimodal-particle-based all-copper interconnects formed at low sintering temperature”

In session 9, “Scaling Cu pillars to 20µm pitch and below: Strategic role of surface finish and barrier layers” presents the first demonstration of Cu pillar interconnections at 20µm pitch, enabled by innovative interconnection designs and advances in surface finish metallurgies with precisely controlled and unique interfacial reactions. The novel surface finish metallurgy, EPAG was introduced in replacement of standard ENEPIG, limited to coarse wiring pitches due to the conventionally high thickness of its Ni layer. This key innovation, combined to the elimination of both the Ni barrier layer between Cu pillar and solder cap and the pre-reflow step, enabled, for the first time, formation of reliable Cu pillar joints with less than 7µm solder height, scalable to 20µm pitch.

The “Morphology study of bimodal-particle-based all-copper interconnects formed at low sintering temperature” in session 21 presents the main advantages of dip based, all-copper interconnect technologies. The compatibility of these technologies with different surface finishes is among the advantages discussed. The highlight is the compatibility of the novel surface finish EPAG, where resistance and shear strength are comparable, and in some cases, better than existing traditional surface finishes. The negative impacts associated with electroless nickel on fine pitch resolution and high frequency applications are resolved by the EPAG process.

To learn more about these technologies, visitors to the ECTC 2017 are invited to attend the presentations and discuss these and other topics with Atotech’s specialists on-site.

Contact

Yvonne Fuetterer

Erasmusstr. 20

10553 Berlin, Germany

+49 30-349 85-220

Yvonne.fuetterer@atotech.com

About Atotech

Atotech is one of the world’s leading manufacturers of specialty chemicals and equipment for the printed circuit board, IC-substrate and semiconductor industries, as well as for the decorative and functional surface finishing industries. Atotech has annual sales of USD1.1 billion. The company is fully committed to sustainability – we develop technologies to minimize waste and to reduce environmental impact. Atotech has its headquarters in Berlin, Germany, and employs more than 4,000 people in over 40 countries.