Halbleiter

Integrierte nasschemische Verfahrens- und Anlagenlösungen für aktuelle und zukünftige Packaging- und Halbleiteranwendungen

Quick facts

- Fortschrittliche Lösungen für Packaginganwendungen – chemische und elektrochemische Abscheidung von Cu, Ni, Pd, Sn, SnAg und Au

- Elektrochemische Lösungen für die neueste Verbindungstechnologie – Damascene-Verfahren mit Cu und Co

- MultiPlate: eine innovative elektrochemische Beschichtungsanlage

- Hightech-Reinraumproduktion

Anwendungen

- Pad-Metallisierung mit ENEPIG für Leistungschips und Speicher

- RDL, Microvias und Pillar-Plating für FOWLP und FC-CSP

- Microvia-TSV-Plating / Filling für Sensoren und 3D-Stacking

- Doppelseitige Metallisierung für Leistungschips wie z.B. IGBT, MOSFETS, etc..

- Verbindungsmetallisierung für Logik-, Speicher- und Leistungs-IC

Produktübersicht

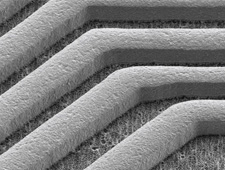

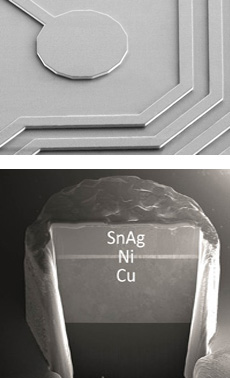

RDL, Microvias und Pillar-Plating für FOWLP und FC-CSP

Ihre Anforderungen:

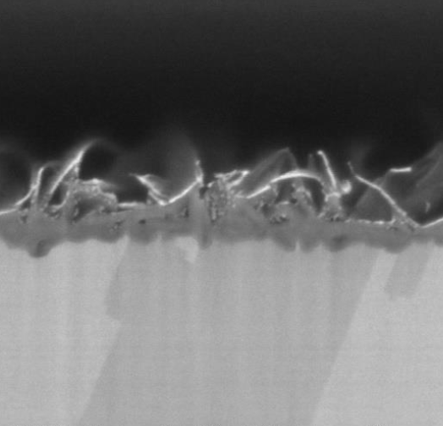

Die neuesten Packaging-Technologien wie FOWLP erfordern diverse Beschichtungslösungen für unterschiedliche Strukturen. Kupfer für Fine-Line-RDL mit und ohne gefüllte Microvias, Cu-Pillars mit und ohne Nickel-Sperrschichten und nicht zuletzt Zinn-Silber für Lötkappen auf Pillars. Um beste Zuverlässigkeiten zu ermöglichen, ist die Reinheit der Kupferschicht entscheidend. Die Reinheit bestimmt die Zuverlässigkeit des gesamten Packages und die Vermeidung vor RDL-Fehlstellen (Cracks) beim Fan-out Wafer Level Packaging oder Mikrovoids/ Lunker an Kupfer/Lot-Verbindungen

Unsere Lösung:

Atotech bietet das komplette Beschichtungssortiment für Pillars, Microvias und Fine-Line-RDL – Hochreine Cu-Schichten für höchste Zuverlässigkeitsanforderungen, seien es RDL, Microvias oder Cu-Pillars. Ein Cu-Elektrolyt für Alles, Beschichtung aller Strukturen / Geometrien Microvias, Fine-Line-RDL und Pillars.

Unsere Produkte:

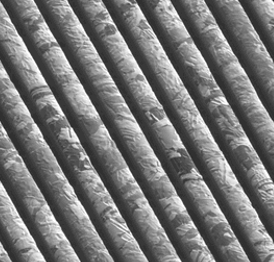

- Spherolyte® Cu UF5: Schnellstes Cu-Pillar Plating mit hervorragenden Homogenitäten

- Spherolyte® Cu UF3: Reinste Performance für Cu-Strukturen wie RDL und µ-Via

- Promobond® AP2: Haftvermittler für die nächste Generation von Packaging Anwendungen

- Spherolyte® Ni: Effektive Sperrschicht zwischen Lot und Cu zur Vermeidung von Hohlräumen

- Spherolyte® SnAg: Zuverlässigste Interconnect Lötanwendungen mit 2 % Ag

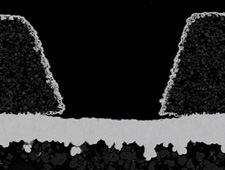

Doppelseitige Metallisierung für Leistungschips wie z.B. IGBT, MOSFET usw.

Ihre Anforderungen:

Moderne IGBT und Leistungs-MOSFET erfordern eine Metallisierung auf beiden Seiten der Wafer. Das herkömmliche Verfahren mit sequenzieller Beschichtung der Vorder- und anschließend der Rückseite sorgt häufig für Spannungen und Verformungen während der Waferbearbeitung. Dünne Wafer, die zum Einbetten von Dies in Power Packages benötigt werden, sind dafür besonders anfällig. Daher ist eine wirksame Reduzierung von Spannungen und Verformungen während der Waferbearbeitung notwendig

Unsere Lösung:

Wir bieten ein Alternativverfahren – gleichzeitige doppelseitige Cu-Beschichtung der Vorder- und Rückseite zur wirksamen Reduzierung der Spannung und Verformung durch:

- Individuelle Steuerung der Cu-Schichtdicke auf Vorder- und Rückseite

- Verarbeitungsmöglichkeit von Taiko-Wafern

- Kurzer Prozessablauf

- Anlagen und Chemikalien aus einer Hand

Unsere Produkte:

MultiPlate® and Spherolyte® MD2: Unser “Dreamteam“ für Leistungs-IC

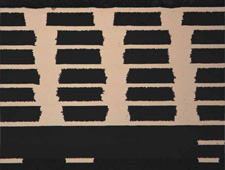

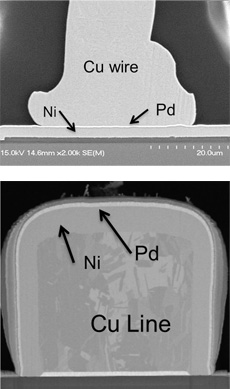

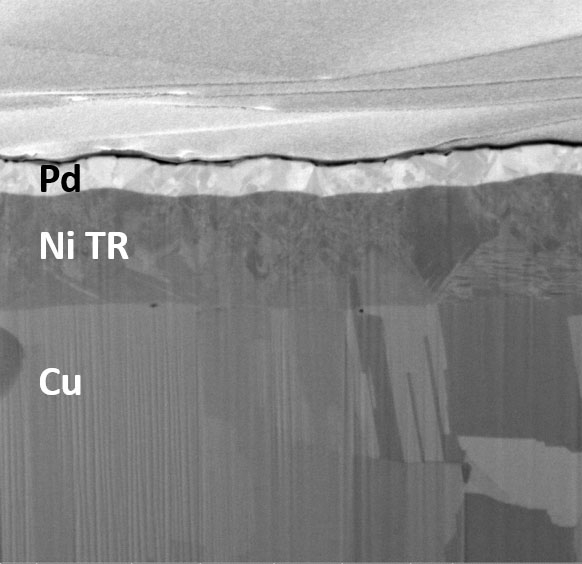

Pad-Metallisierung und RDL-Housing

Ihre Anforderungen:

Drahtbonden oder Löten – welche Oberfläche ist für Ihre Packaging-Anforderungen am besten geeignet? Und wie bekommt man den gewünschten Metall-Stack auf den Al- oder Cu-Wafer? Ist dies auch in der Massenproduktion möglich? Ist das Verfahren zuverlässig, bewährt in der Automobilbranche oder in noch anspruchsvolleren Umgebungen? All dies sind die typischen Fragen und Herausforderungen, die letztlich bestimmen, welche Metalle für First-Level-Verbindungen verarbeitet werden sollen.

Unsere Lösung:

- Universelle Vorbehandlung, d.h. Zinkatierungsprozesse für alle Al-Legierungen und universelle Aktivierung für Cu-Wafer

- Automotive-erprobte ENEPIG-Stacks (chemisch Ni – chemisch Pd – Sudgold)

- Hochproduktive Prozesse für Nassprozess- anlagen, die 25 oder 50 Wafer auf einmal verarbeiten können.

- Cyanidfreie Verfahren

- Hochtemperaturfeste ternäre Ni-Schichten

- Reine Pd-Schichten für erhöhte Zuverlässigkeit

Unsere Produkte:

- Xenolyte® Pd HS: Reines Pd für qualitativ hochwertige Drahtbondanwendungen

- Xenolyte® Ni TR: Ternäre Ni-Schicht für hohe Temperaturfestigkeit

- Xenolyte® Au CF2: Cyanidfreies Sudgoldverfahren

Verbindungsmetallisierungslösungen für Logik-, Speicher- und Leistungs-IC

Ihre Anforderungen:

Verbindungstechnologien der nächsten Generation erfordern extreme Leistungen von Nassmetallisierungsverfahren

- Kompatibel mit extrem dünnen „Seed Layern“ für BEOL-Kupferverbindungen in der Damascene-Technik

- Filling Möglichkeit für Öffnungen der Vorbeschichtung von weit unter 10 nm sowohl für Kupfer- als auch für Kobaltverbindungen

- Void-/ Lunkerfreie, hochreine Cu- und Co-Schichten

Von größter Bedeutung ist die void-/lunkerfreie Füllung der Verbindungen. Immer dichtere und komplexere Schaltverbindungen erfordern eine immer höhere Fertigungspräzision.

Unsere Lösung:

- Atotech bietet, nach neustem Stand der Technik, Chemikalien für die Nassmetallisierung von Cu- und Co-Verbindungen an.

- Extreme Reinheitsanforderungen werden von den von uns entwickelten Chemikalien mühelos erfüllt.

- Für jeden Metallisierungsschritt sind Lösungen verfügbar, die mit allen modernen ECD-Plattformen kompatibel sind.

Unsere Produkte:

- Everplate® 2XT: Hochleistungsfähiges Additivpaket für die Cu –Filling Technologie mittels zukunftsorientierter Damascene-Technik

- Atomplate® Co: Elektrolytisches, reines Co für MEOL-Verbindungstechnologien, welches ein echtes Bottom-up-Filling ermöglicht

Featured products

Spherolyte® Cu UF5

Schnellstes -Cu-Pillar Plating mit hervorragenden Homogenitäten

Spherolyte® Cu UF3

Universelle Plating Chemie für Cu Strukturen wie RDL und Micro Via Filling

Promobond® AP2

Haftvermittler für die nächste Generation von Packaging Anwendungen

Xenolyte® Ni TR

Verbesserte Chemie für breit einsetzbare und stressarme stromlose Ni-Abscheidung

Spherolyte® Cu UF 5

Schnellstes Cu-Pillar Plating mit hervorragenden Homogenitäten

Mit Spherolyte® Cu UF 5 sind wir mehr als bereit, die härtesten Anforderungen an die Gleichmäßigkeit mit einem neuen, reinen und gleichmäßigen Kupfersäulen-Abscheidungsprozess zu erfüllen, der mit den höchsten Beschichtungsgeschwindigkeiten arbeiten kann.

Hochreine Prozesschemikalien

Reinraumfertigung für die Halbleiterindustrie

Unsere hochreinen Chemikalien werden nach den aktuellsten und strengsten Vorgaben der Halbleiterindustrie gefertigt. Die Herstellung und Reinraumabfüllung erfolgt am Standort Neuruppin auf einer Fläche von 1.500 m² in einer geschlossen Produktionsumgebung auf vollautomatisierten Fertigungsanlagen. Dies garantiert eine effiziente, umweltfreundliche, sichere und wirtschaftliche Produktion.

“We continuously strive to provide best-in-class metallization solutions to the semiconductor industry. This makes us a valuable partner for the development of next generation technologies.“

Dr. Christian Ohde

Global Product Director Semiconductor Advanced Packaging Products at Atotech Germany

Recent publications

An innovative plating system for next generation packaging technologies

This article was originally published in Silicon Semiconductor.

As device geometries continue to shrink, semiconductor packaging technologies face constant challenges to remain relevant and economically viable. Need of the hour is to develop innovative approaches that cost-effectively address the emerging requirements. This article will explore the current challenges for advanced packaging and how they may be overcame by rethinking traditional manufacturing approaches.

2016, PDF, 3,400 KB

Fan-out packaging: a key enabler for optimal performance in mobile devices

This article was originally published in Chip Scale Review.

The emergence of FOWLP has been directly linked to satisfying the requirements for consumer electronics, and particularly those of mobile devices. This article will explore the drivers behind fan-out packaging, the key processing challenges, and the requirements at the application level. It will also discuss why fan-out is the ideal packaging technology for future generation mobile devices, and will present a turnkey solution for manufacture within both wafer and panel formats.

2017, PDF, 1,200 KB

Next-generation copper pillar plating technologies

This article was originally published in Chip Scale Review.

As the industry moves towards smaller, faster devices, there is mounting pressure on all members of the supply chain to enable higher performance at lower cost.

The limitations of Moore’s Law are evident and advanced technology nodes are no longer providing a significant cost benefit. As a result, the industry has shifted its focus to advanced packaging as a means for providing enhanced performance and lower costs, i.e. “More than Moore.“

The primary drivers for this shift are improved performance, more functionality, and cost reduction. This article will discuss how these three drivers have led to the emergence of flip-chip packaging using pillars and the current and future challenges for Cu pillar technology.

2016, PDF, 560 KB

The Interactions between SNAGCU Solder and NI(P)/AU, NI(P)/PD/AU UBMS

Investigations of intermetallic reactions between the Sn3.5Ag0.5Cu solder and two different UBM structures, Ni(P)/Au and Ni(P)/Pd/Au.

2015, PDF, 2,250 KB