Semiconductor

Integrated wet chemical processes for pad metallization, copper pillar, RDL, vias and dual damascene

Quick facts

- Electrochemical deposition processes and equipment solutions

- Plating processes for RDL, vias, pillars and solder applications for next generation advanced packaging

- Electroless deposition processes for pad metallization and RDL housing, e.g., in power semiconductor applications

- Electrochemical solutions for dual damascene plating for latest interconnect technology

- State-of-the-art manufacturing site in Germany

Applications

- Pad metallization with ENEPIG for power chips and memory

- RDL, µ-vias and pillar plating for FOWLP and FC-CSP

- µ-via and through silicon via plating for sensors and 3D stacking

- Double sided metallization for power chips , e.g., IGBT, MOSFETS…

- Interconnect metallization for logic, memory and power ICs

Product portfolio

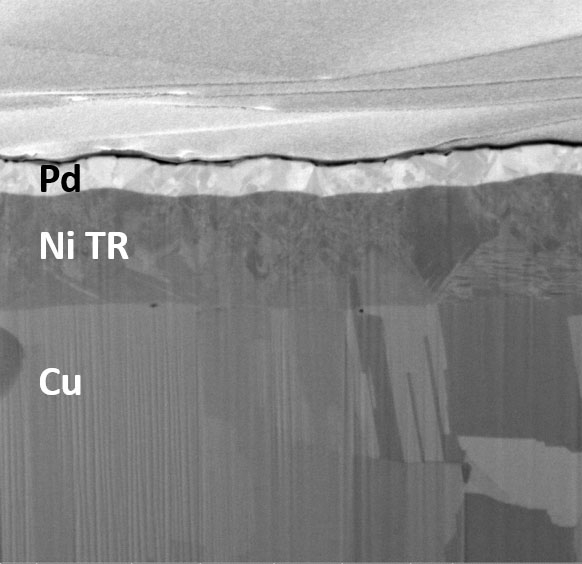

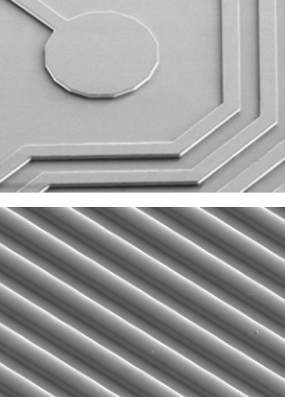

Advanced packaging – RDL and µ-Via plating

Latest packaging technologies such as FOWLP and FC-CSP require a variety of plating solutions for different structures. Fine line RDL allows the electrical extension within the plane and are hence crucial to enable heterogeneous integration.

- Spherolyte® Cu UF3: high purity Cu process for the deposition of RDL & µ-via of highest reliabilities.

- Promobond® AP2: adhesion promoter for next generation packaging.

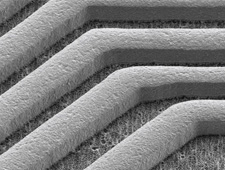

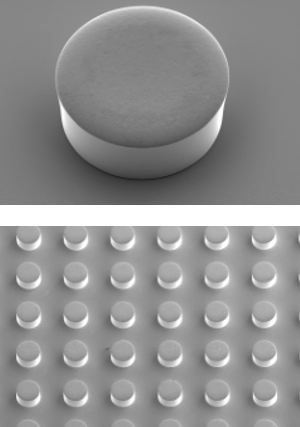

Advanced packaging – Pillar plating and soldering

Latest packaging technologies such as FOWLP and FC-CSP require a variety of plating solutions for different structures. Pillars and solderbumps are used for interface interconnection and are hence crucial to enable heterogeneous integration.

- Spherolyte® Cu UF 5: high-speed process for Cu pillar plating with outstanding uniformities, high purity and full shape control.

- Spherolyte® Ni: all liquid process for effective Ni barrier layer plating.

- Spherolyte® NiFe: all-liquid ECD NiFe electrolyte for barrier plating and electromagnetic shielding.

- Spherolyte® SnAg: highly uniform and reliable tin silver process for solder applications.

- Spherolyte® Sn: process for highly uniform, pure tin solder depot plating.

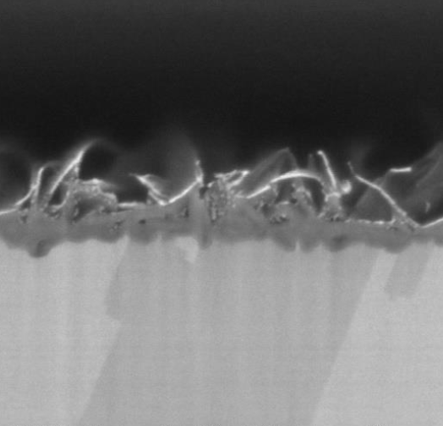

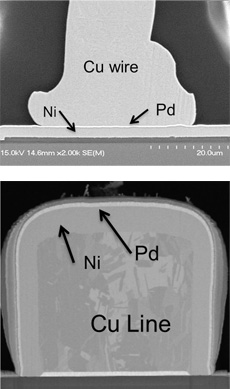

ENEPIG plating - pad metallization and RDL housing

Wire bonding and soldering often require under bump metallization (UBM) for highly reliable joint formation. Our Xenolyte® product suite allows the deposition of hard, corrosion-free, and stress-minimized metal stacks to protect underlying active structures and provide a robust, stable, and low-resistance solder joint connection to the IC substrate.

- Xenolyte® Ni: processes for low- to mid Pd and high-temperature electroless Ni plating.

- Xenolyte® Pd: electroless deposition process of pure, highly reliable Pd.

- Xenolyte® Au: cyanide-free and cyanide-based immersion and autocatalytic Au processes.

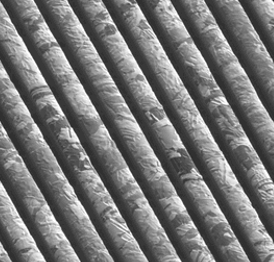

Interconnect metallization solutions for logic, memory and power ICs

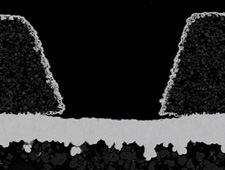

Next generation interconnect technologies demand extreme performance of wet metallization processes which are compatible with extremely thin seed layers for copper damascene BEOL interconnects and able to void-free fill pre-plate openings for both copper and cobalt interconnects.

Everplate® 2XT: high performance additive suite capable of filling advanced damascene Cu technology nodes.

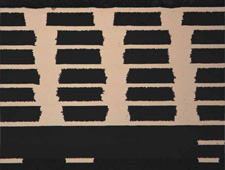

Double sided metallization for power chips, e.g. IGBT, MOSFETS...

Modern IGBTs and power MOSFETs require metallization on both sides of a wafer. The standard way of sequentially plating first front and then backside often struggles with stress and warpage issues during wafer processing. Thin wafers, needed to embed dies in power packages, are especially prone to this effect. What we need is an effective stress and warpage reduction during wafer processing.

MultiPlate® + Spherolyte® MD2: plating equipment solution and electrolytical deposition Cu process for simultaneous double side Cu plating with reduced process flow.

Featured products

Spherolyte® Cu UF5

High speed Cu pillar plating with outstanding uniformities

Spherolyte® Cu UF3

Universal Cu plating suite for RDL and micro via filling

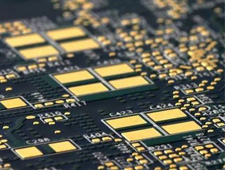

MKS’ Atotech semiconductor plating solutions

We offer market leading solutions for advanced packaging and power semiconductor applications.

This image video gives some impressions of our Spherolyte® and Xenolyte® process solutions that enable our customers to produce state-of-the-art and next generation semiconductor devices.

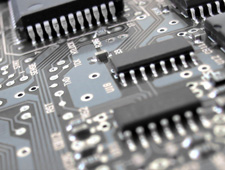

High purity chemistry production

Manufacturing for the semiconductor industry

We produce high purity chemistry according to the latest and most stringent semiconductor industry requirements. Our 1,500m² manufacturing facility located near Berlin in Germany is equipped with highly automated manufacturing equipment and enclosed production environments to ensure efficient, safe, environmental friendly and reliable production.